Project information

- Project date: April 7, 2025- April 21, 2025

- Tools: Cadence Virtuoso (Schematic & Layout)

Summary

1kB 6T SRAM Design – Cadence Virtuoso VLSI Project (April 2025)

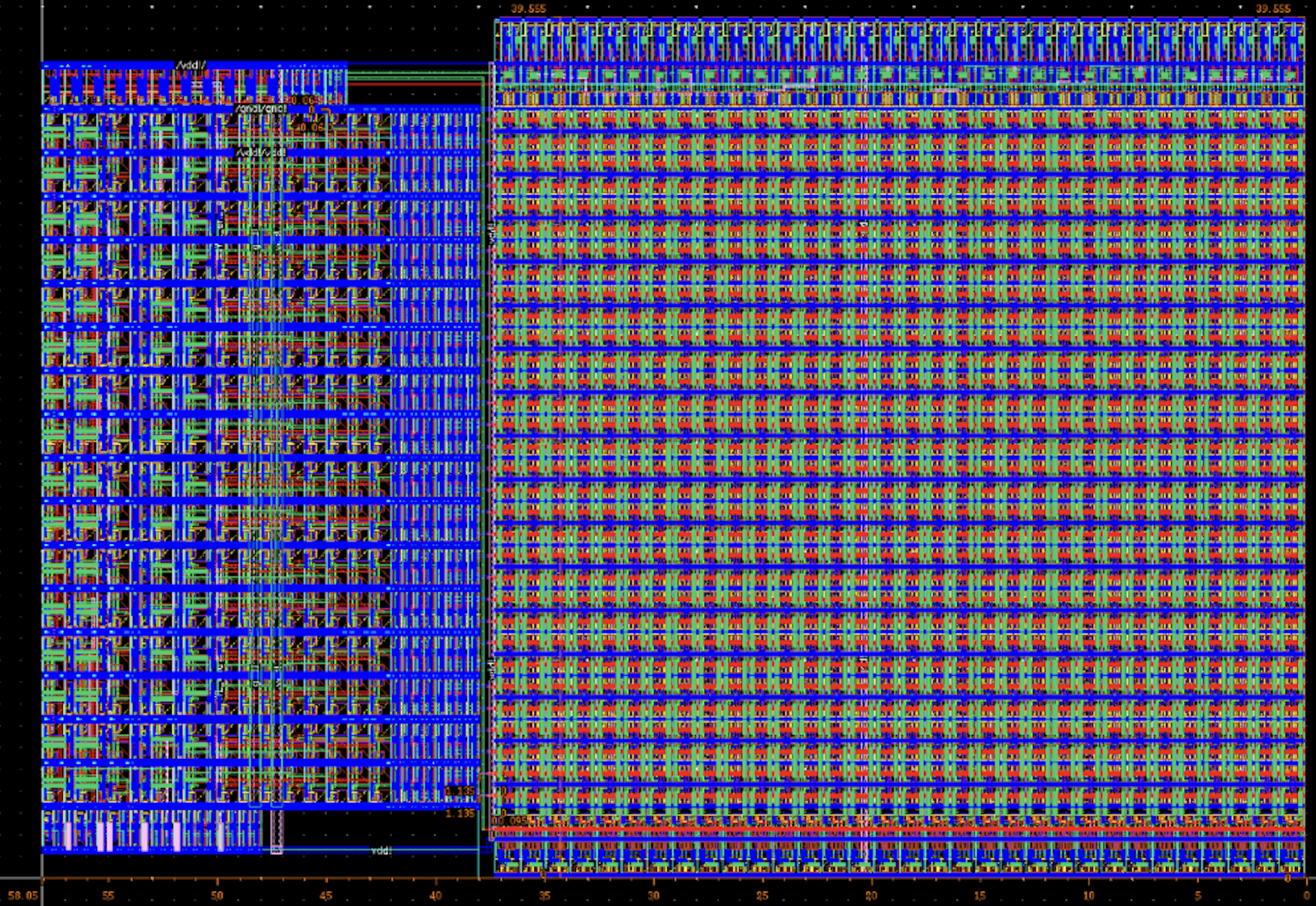

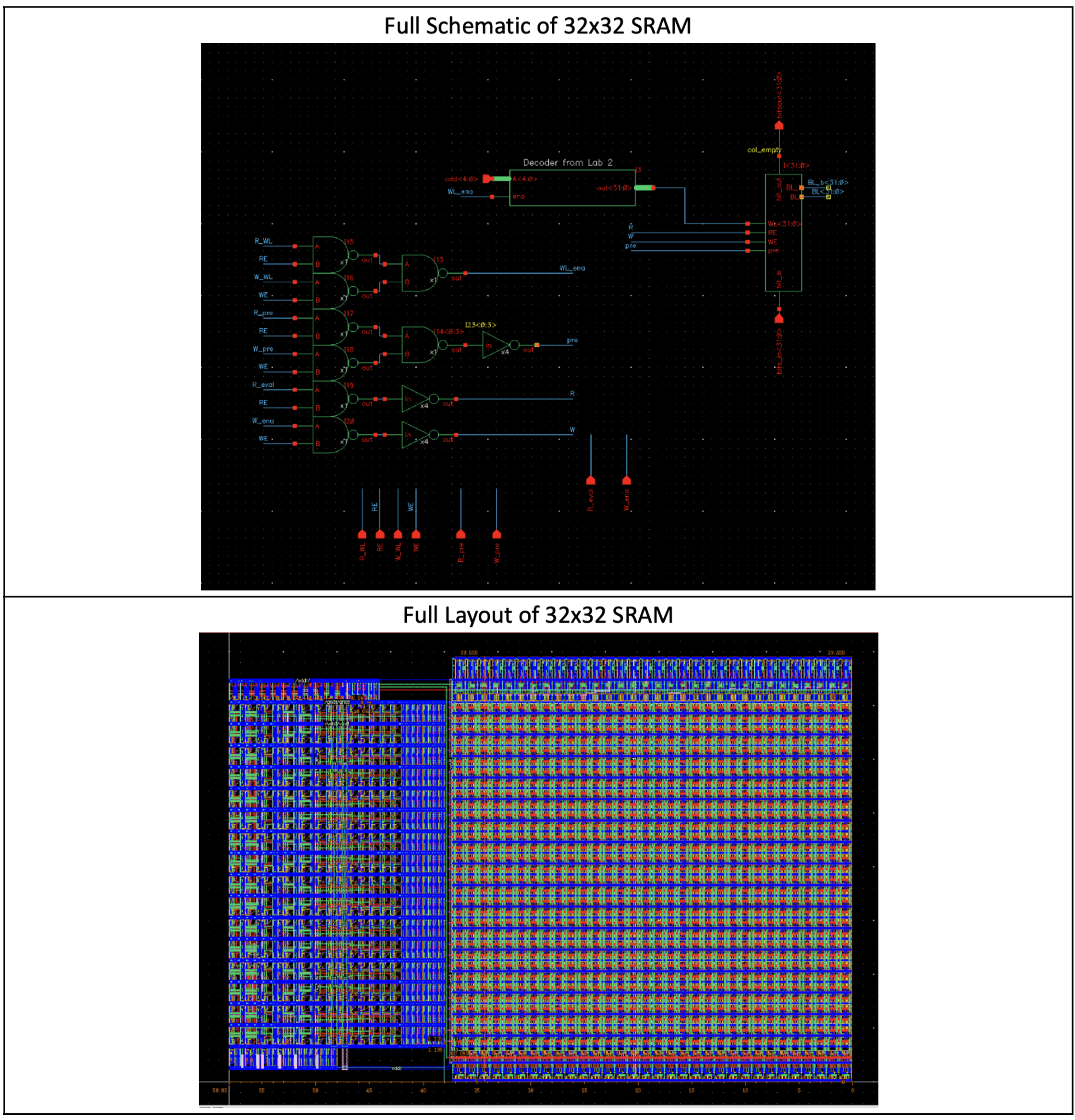

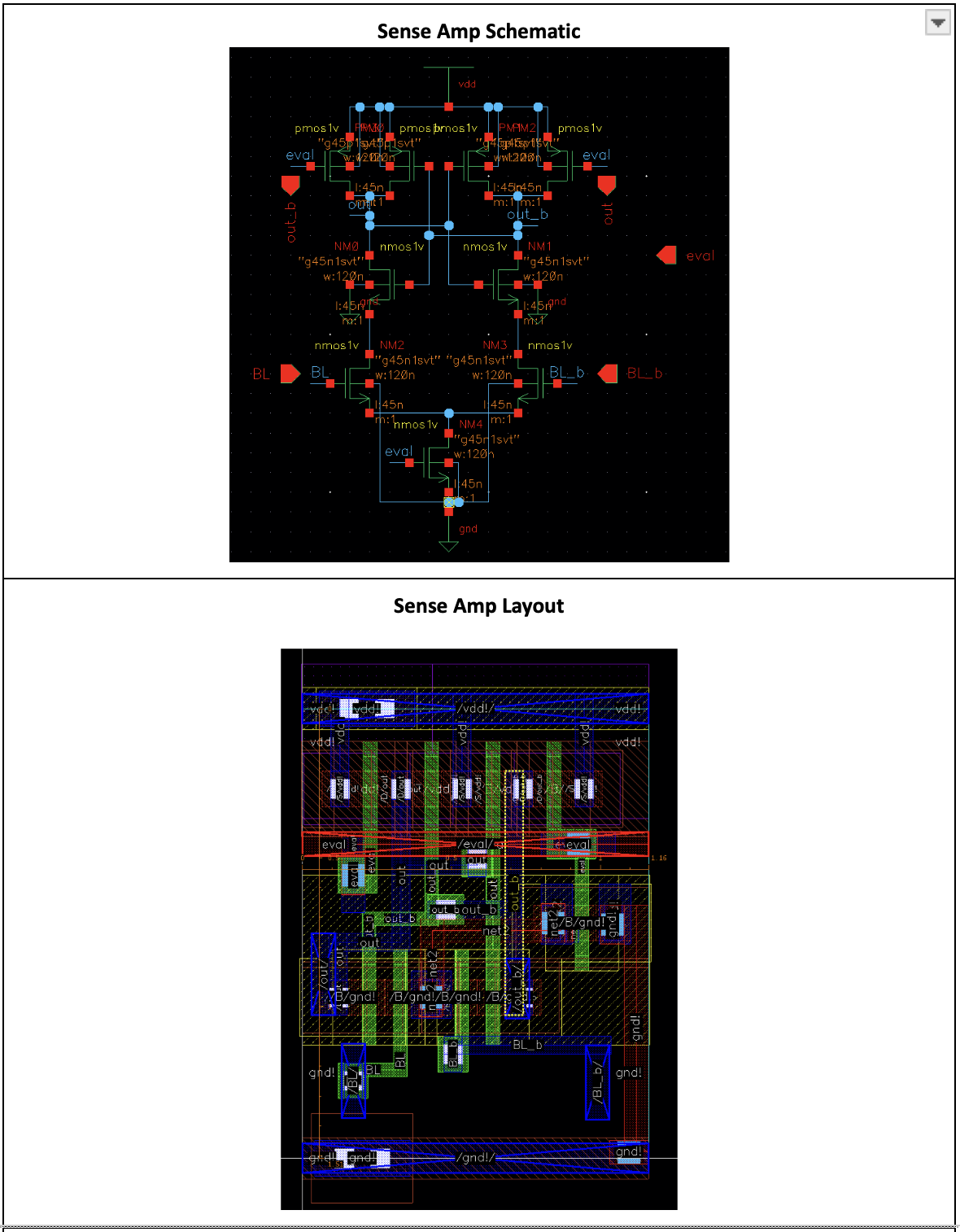

As part of my digital VLSI design course, I developed a 1 kilobyte (32×32) 6T SRAM array from schematic to layout using Cadence Virtuoso. This included designing and verifying memory cells, integrating a 5-to-32 decoder for wordline selection, and optimizing the layout for performance and area.

Post-layout simulations confirmed a 600ps cycle time with a read energy of just 14.2fJ/bit. I ensured full read/write functionality through schematic simulation and resolved extensive DRC/LVS issues during layout verification.

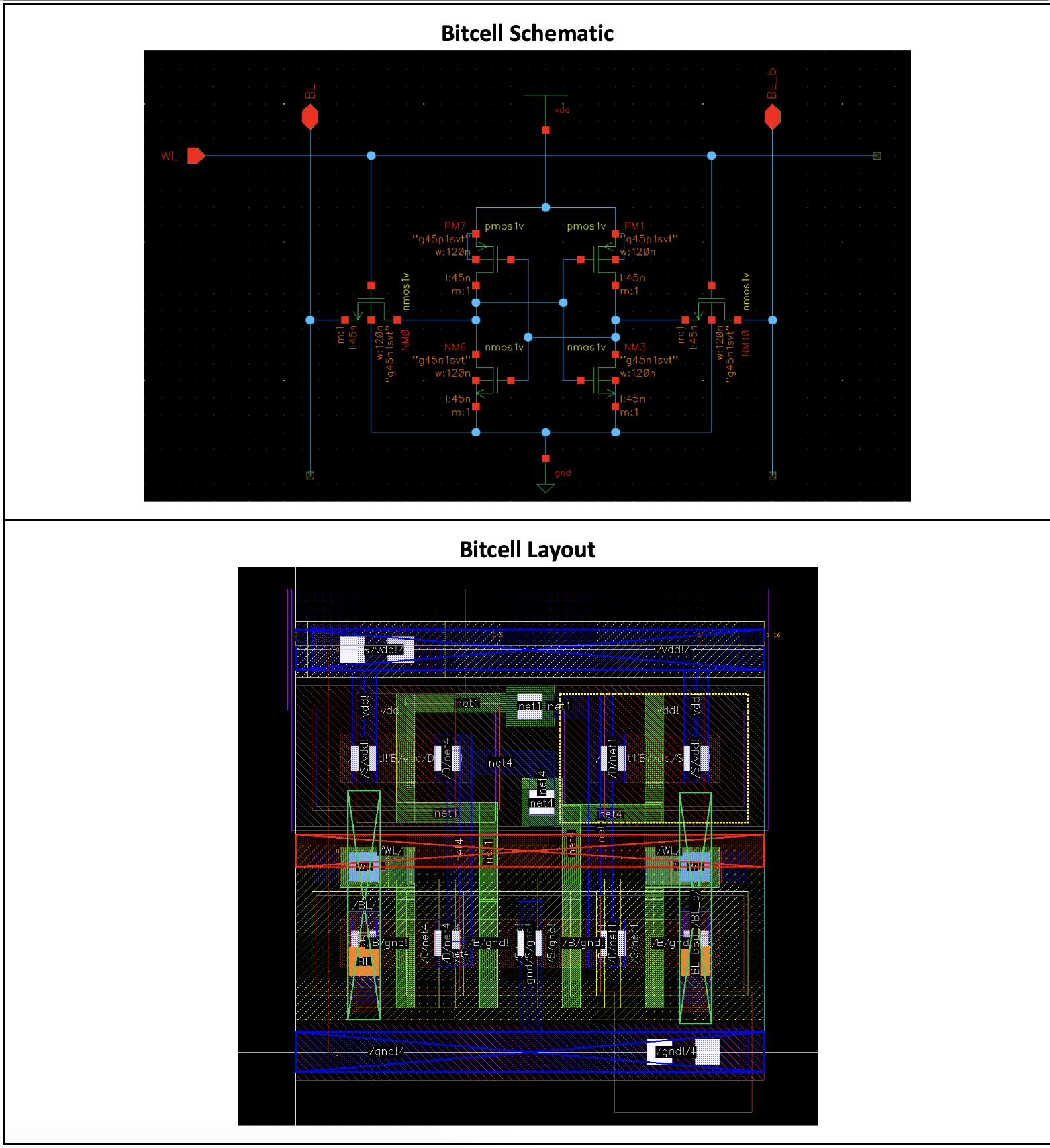

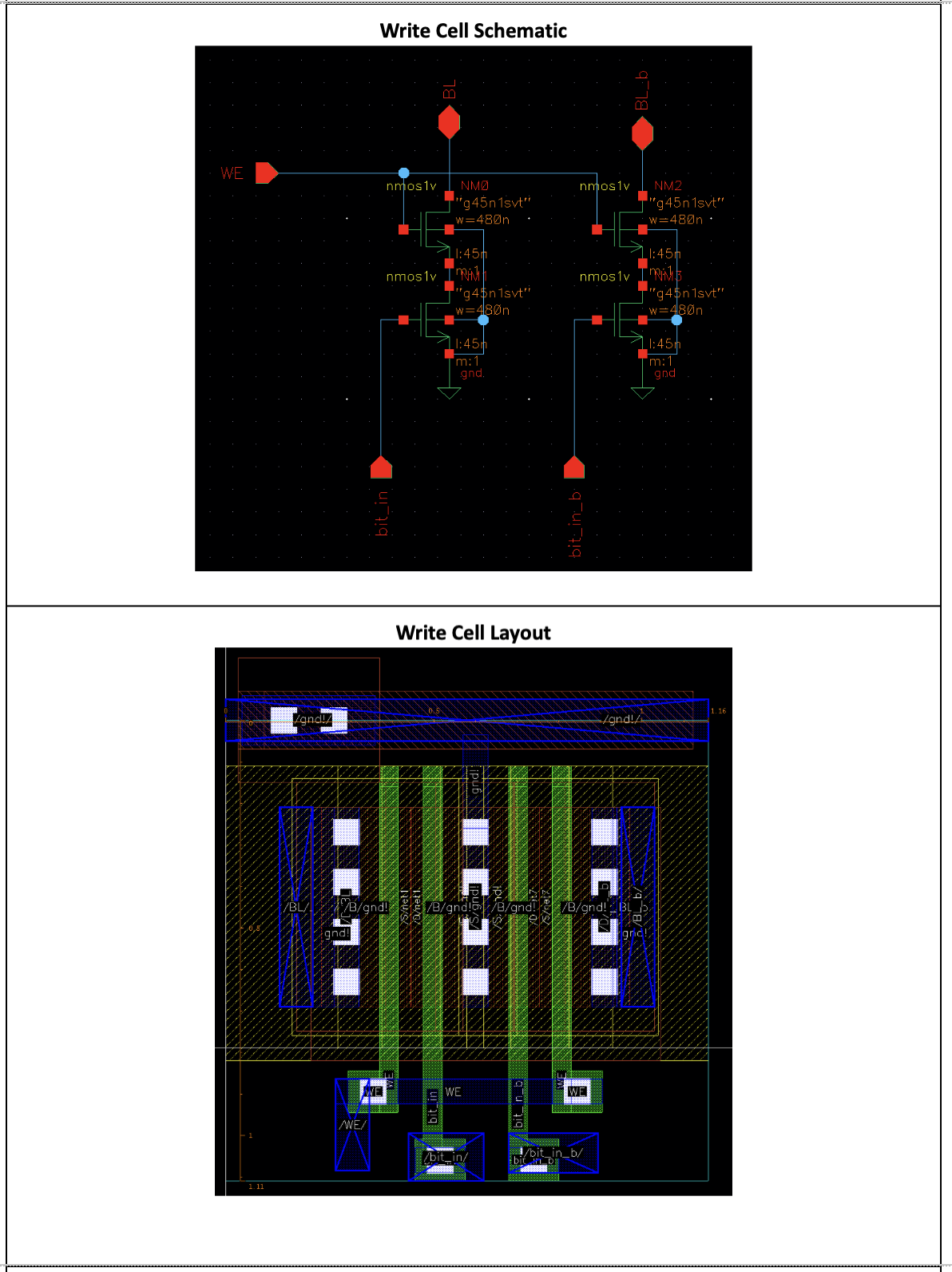

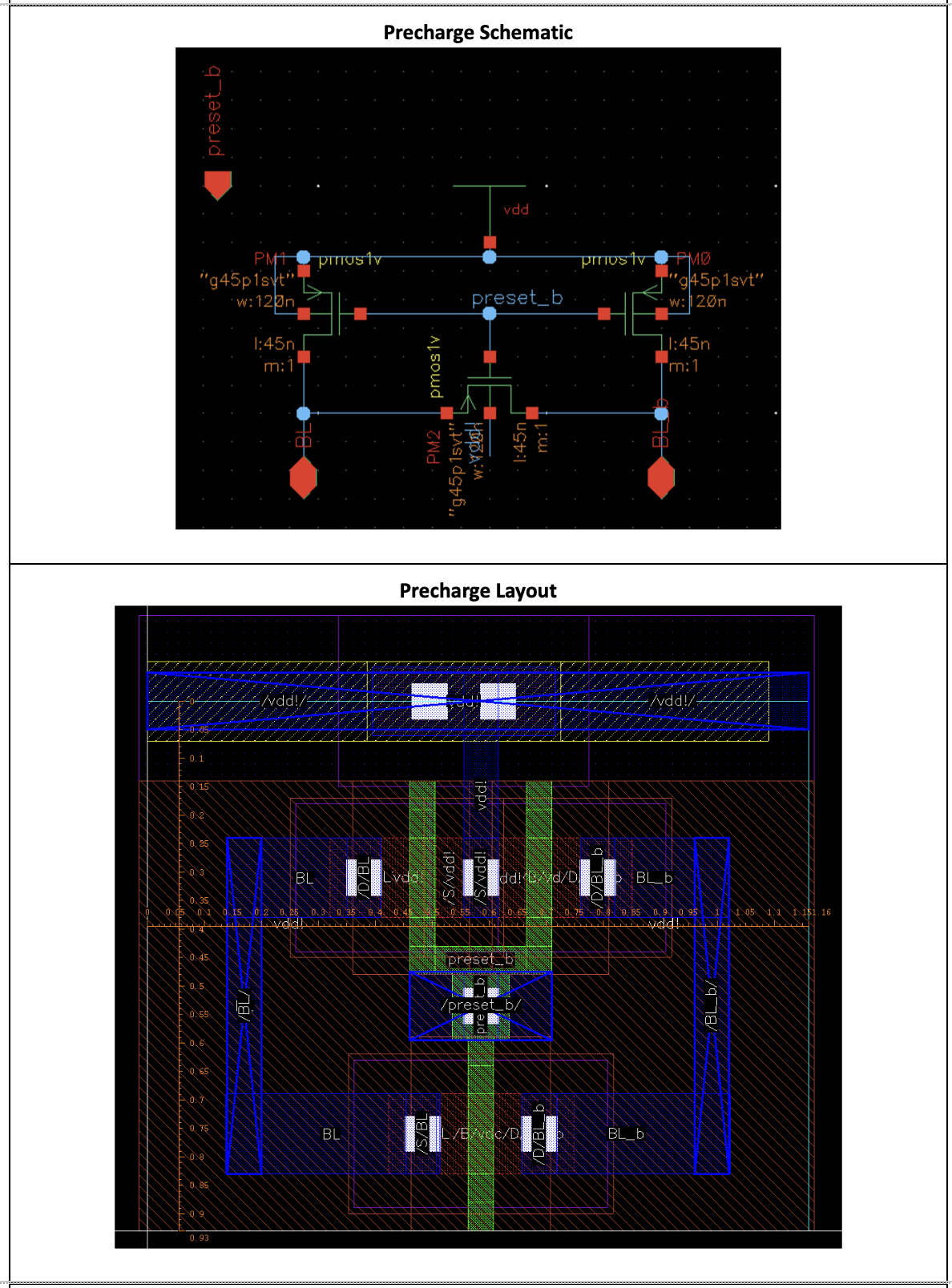

Our team parallelized work with one person building and verifying each of the following:

->Bitcell

->Sense Amp

->Write cell

->Precharge - I was responsible for devising a compact Precarge cell to minmal array area

These were follwed up by thorough 32 bit column testing, MonteCarlo Simulations then the final Full Layou simulations.