Project information

- Project date: Sept. 1st, 2024- Dec. 18th, 2024

- Lanugage: Verilog HDL

- Tools: PyMTL, RTL Design

Summary

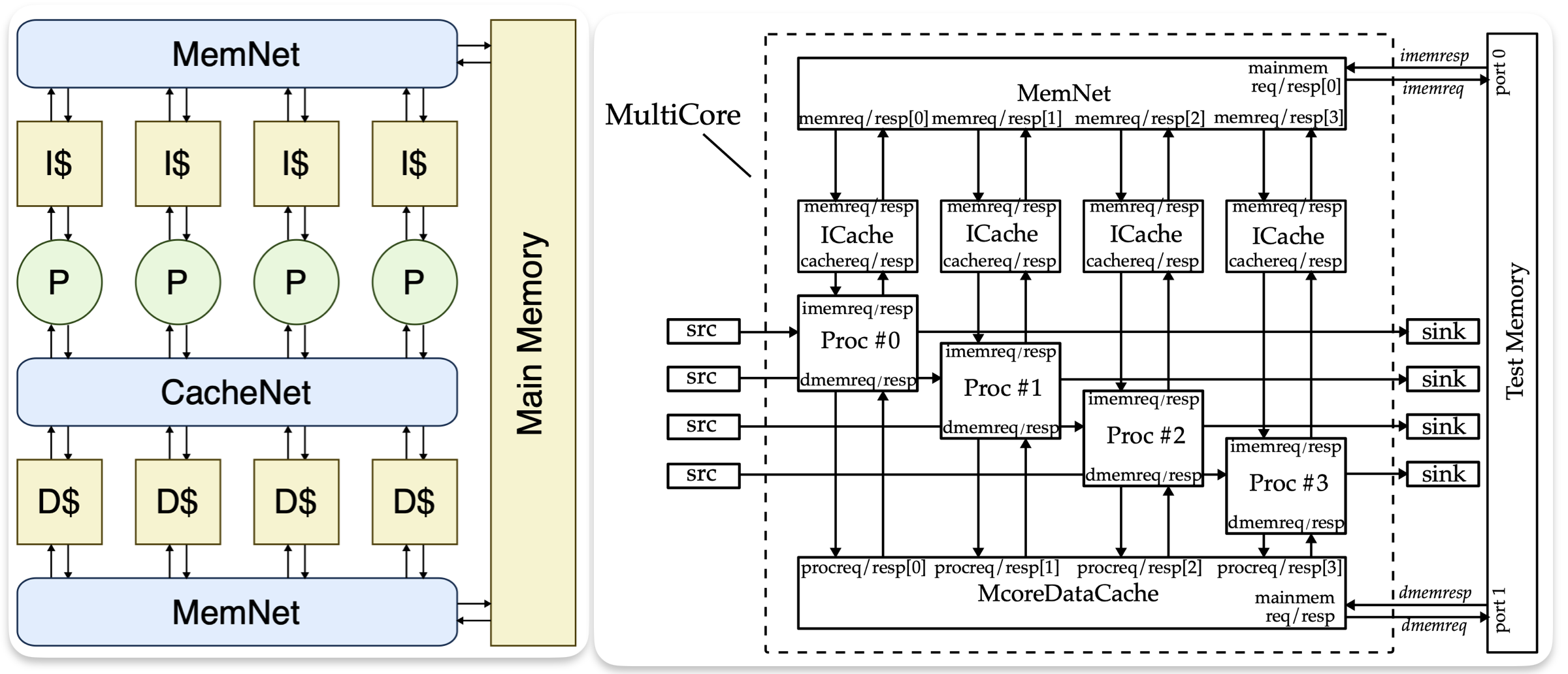

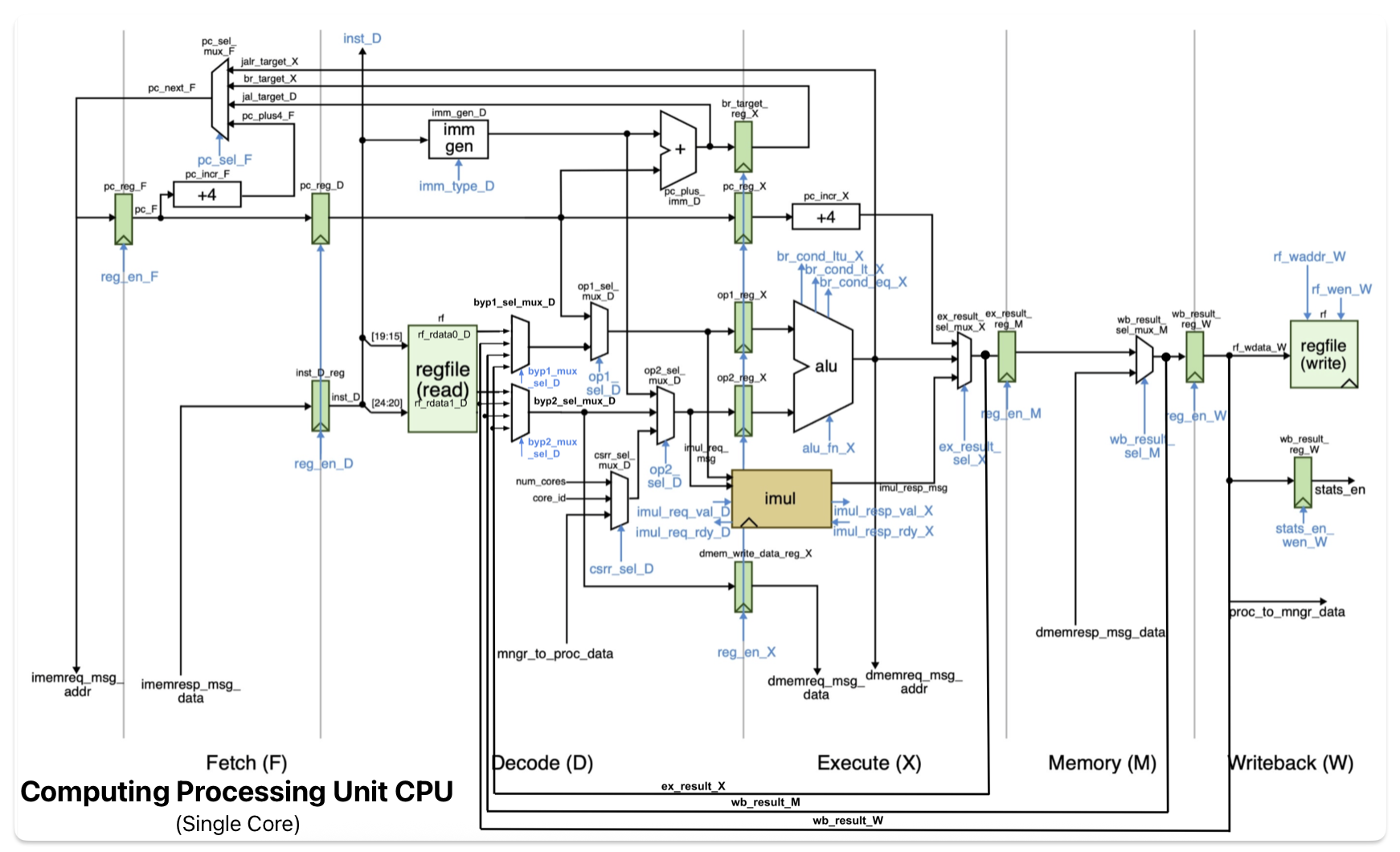

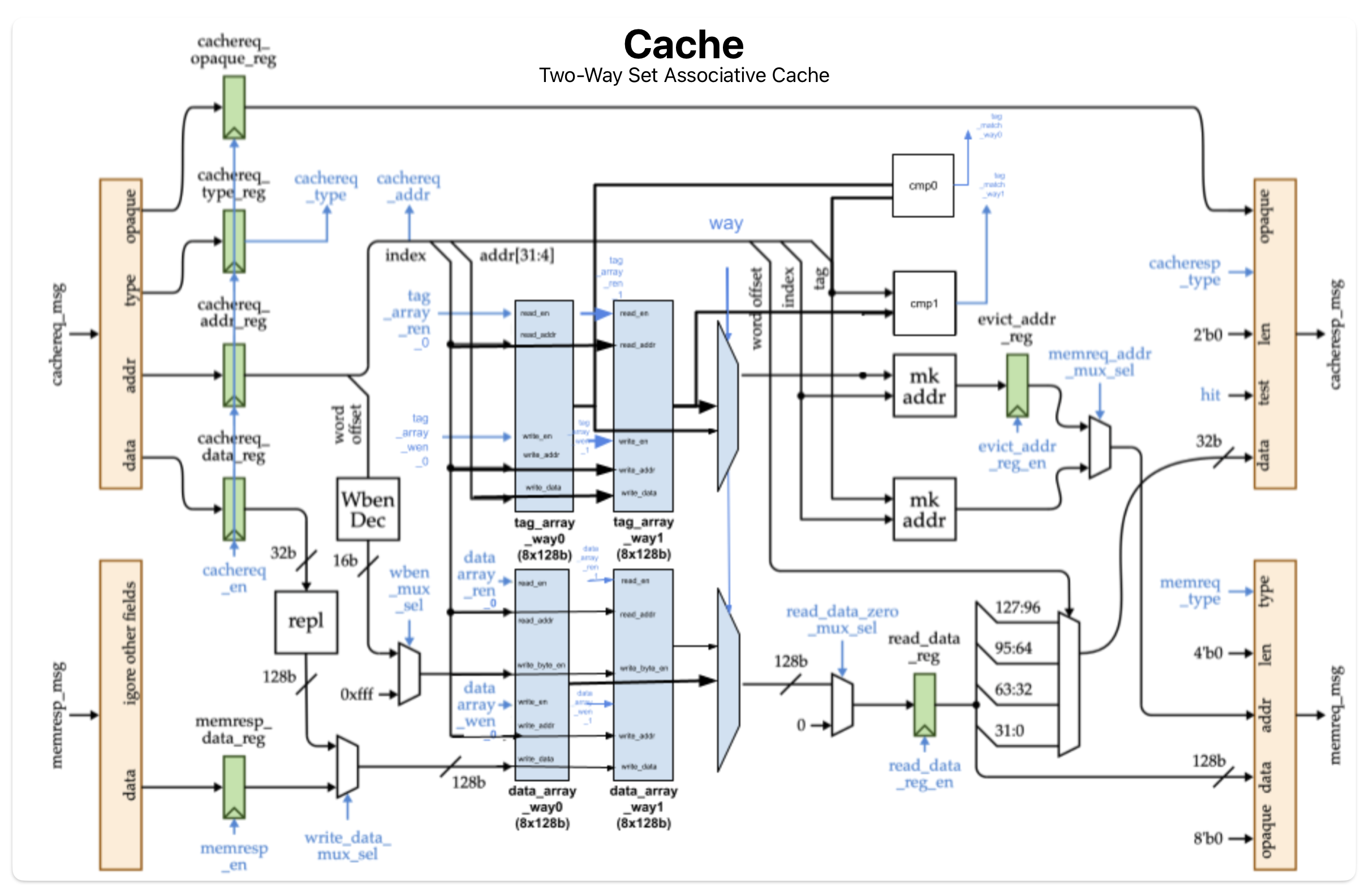

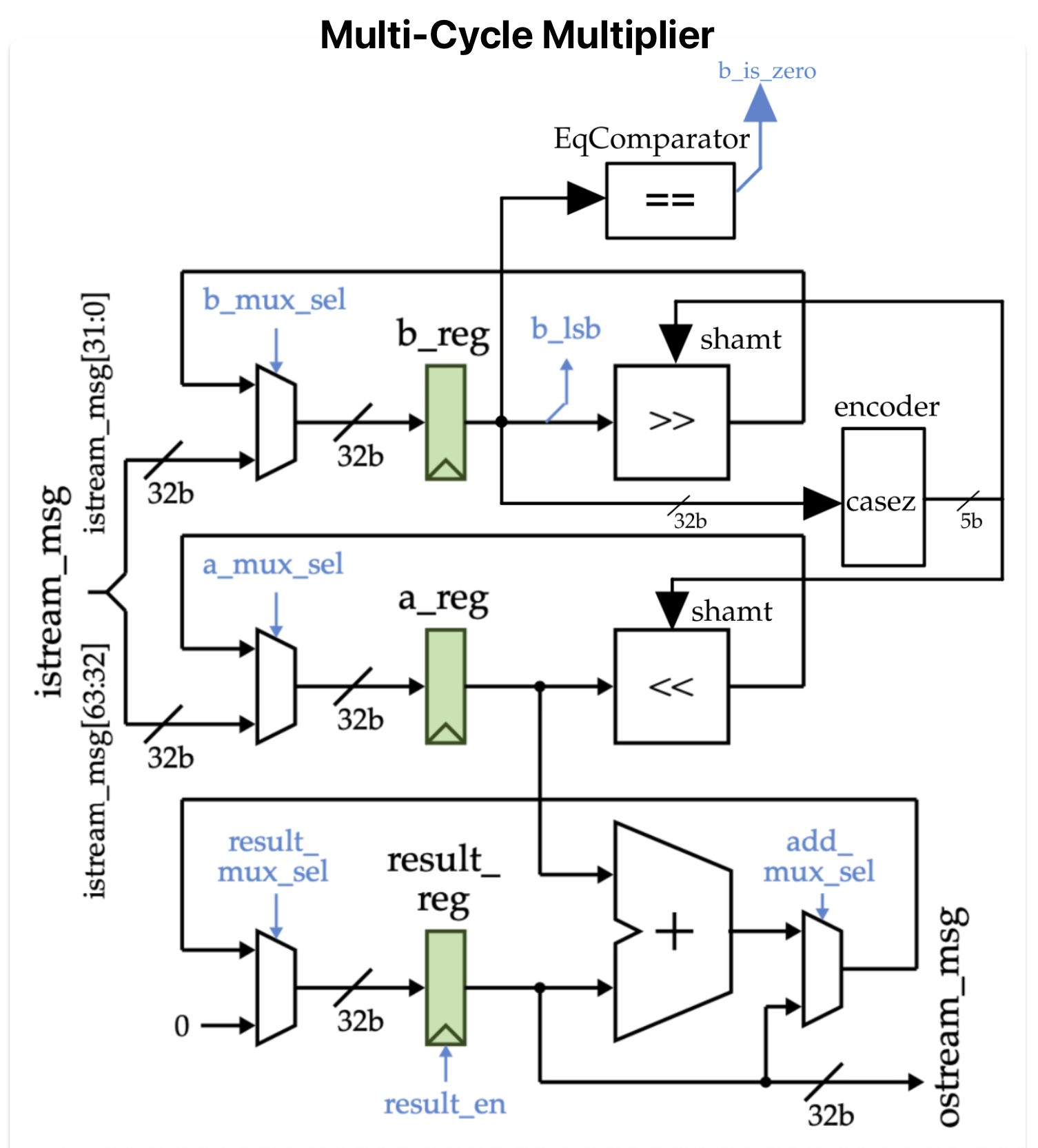

Multicore Pipelined RISC-V Processor – Computer Architecture Culminating Design (Fall 2024) Designed and implemented a multicore, pipelined RISC-V processor in Verilog HDL with full bypassing and multi-cycle execution. I optimized memory performance by building a custom cache and explored trade-offs in area, energy, and speed across design variants—finding that bypassing improved execution speed by ~50%. Functionality was rigorously verified using Python-based testbenches, hazard resolution, and execution trace analysis with PyMTL.