Project information

- Project date: February 9, 2026 - February 23, 2026

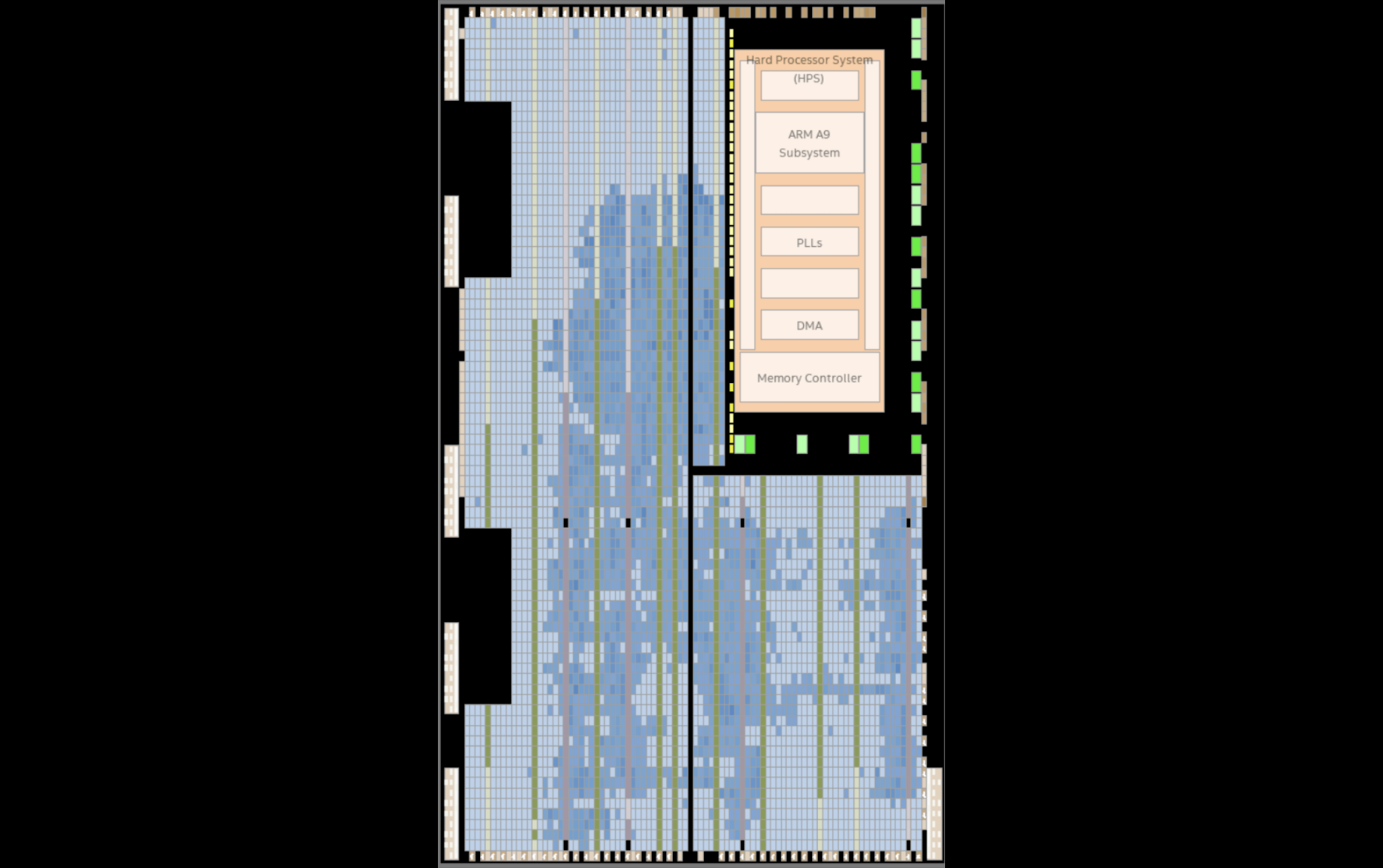

- Tools: Intel Quartus, Intel Altera DE1-SoC FPGA, ModelSim, Qsys

- Link to YouTube Video

- Link to Lab Report

Summary

Mandelbrot Set Visualizer

VGA Pixel Render Parallelization

FPGA Design Project

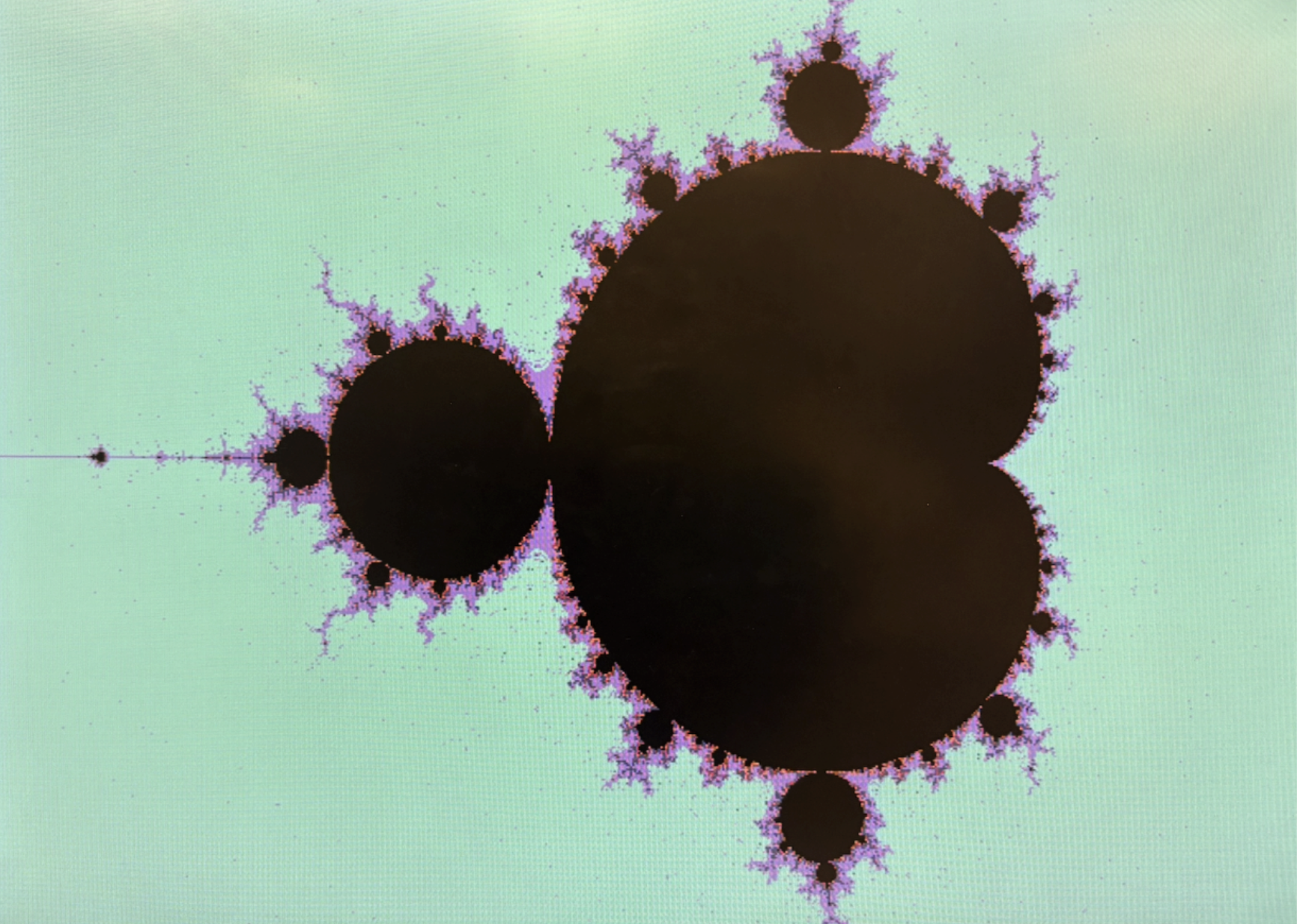

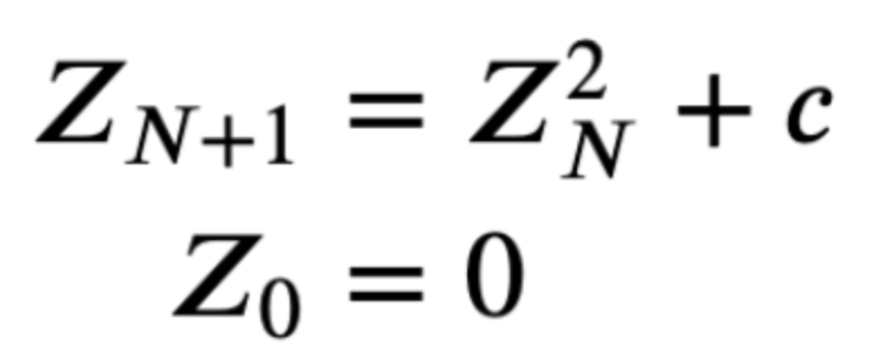

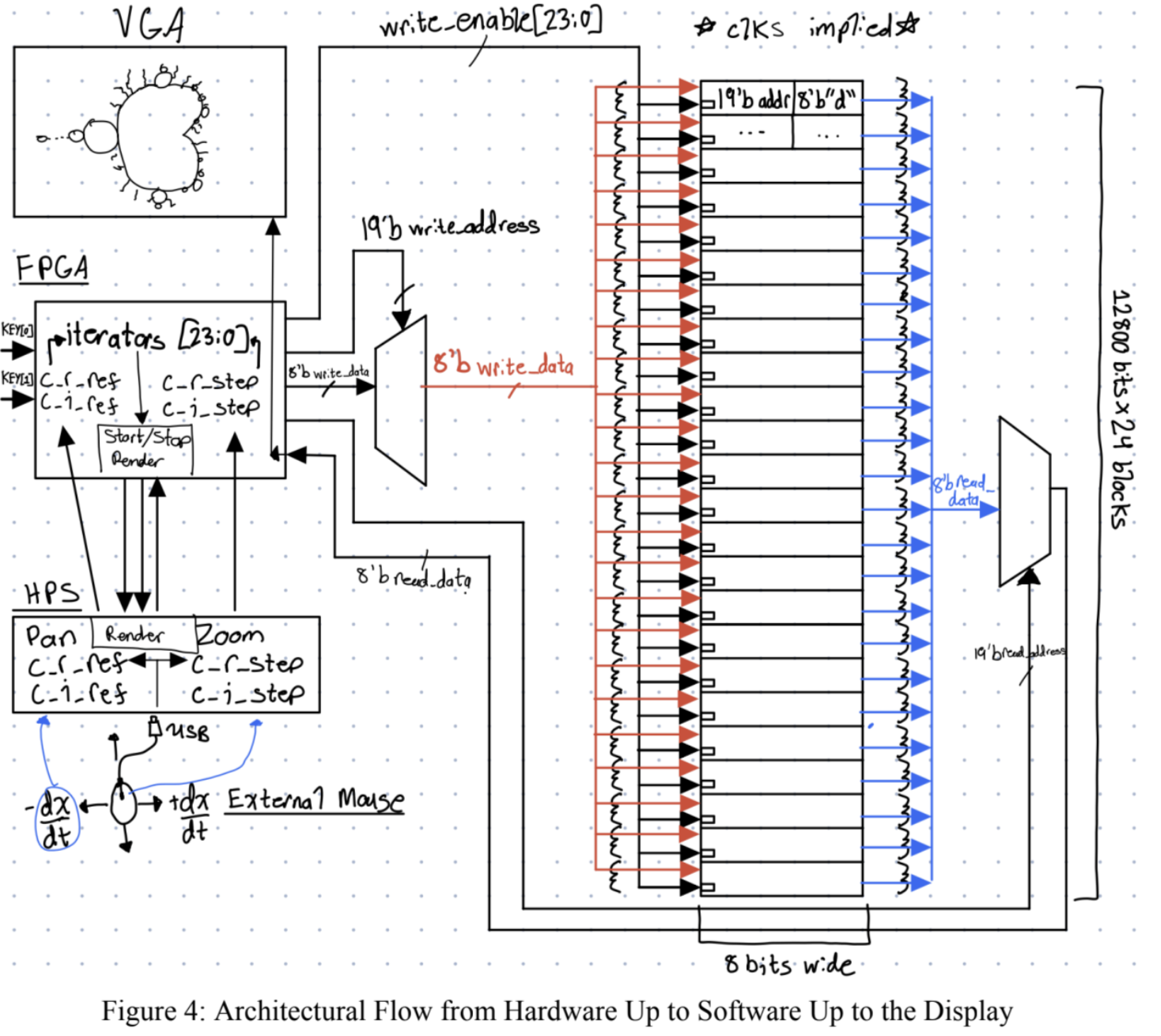

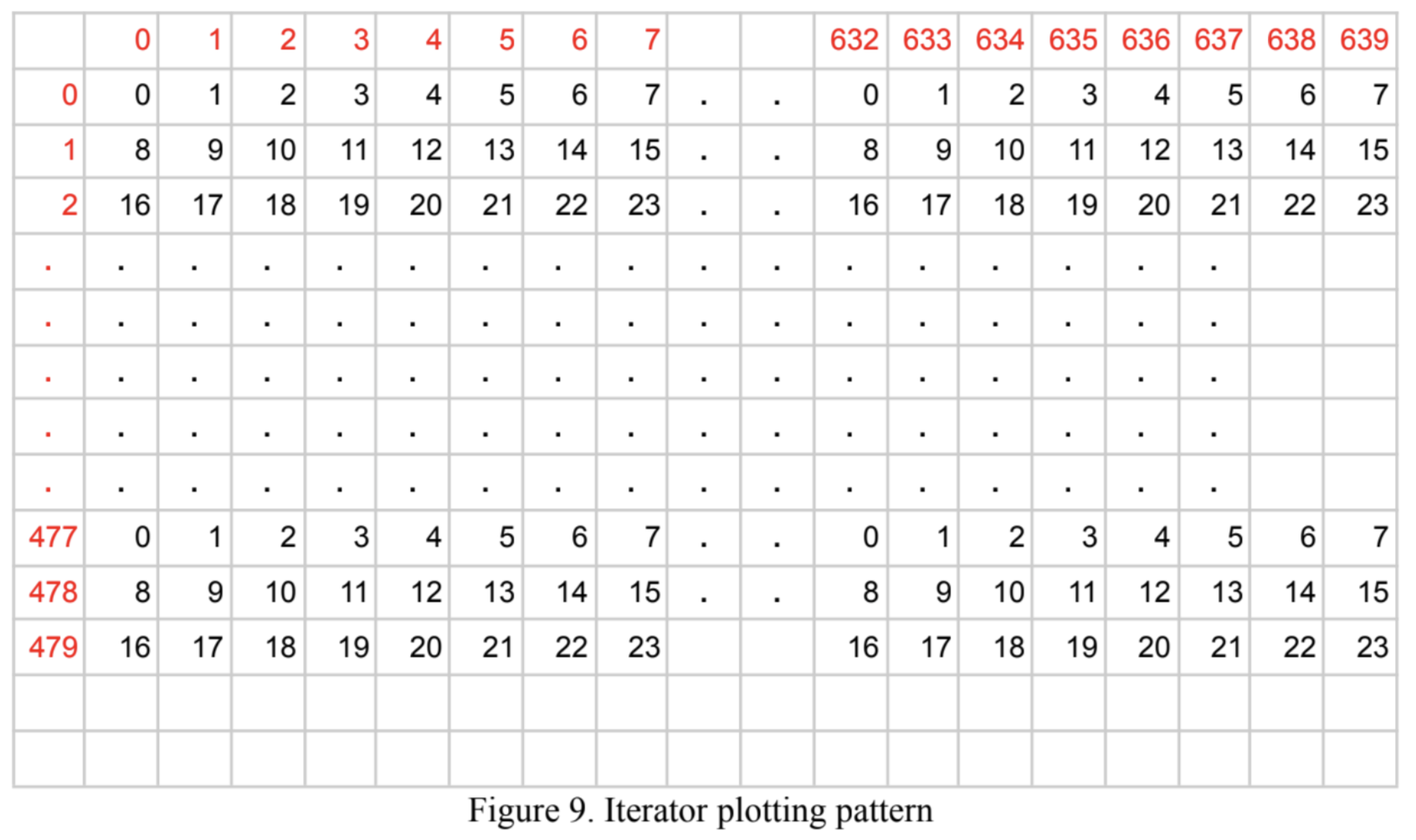

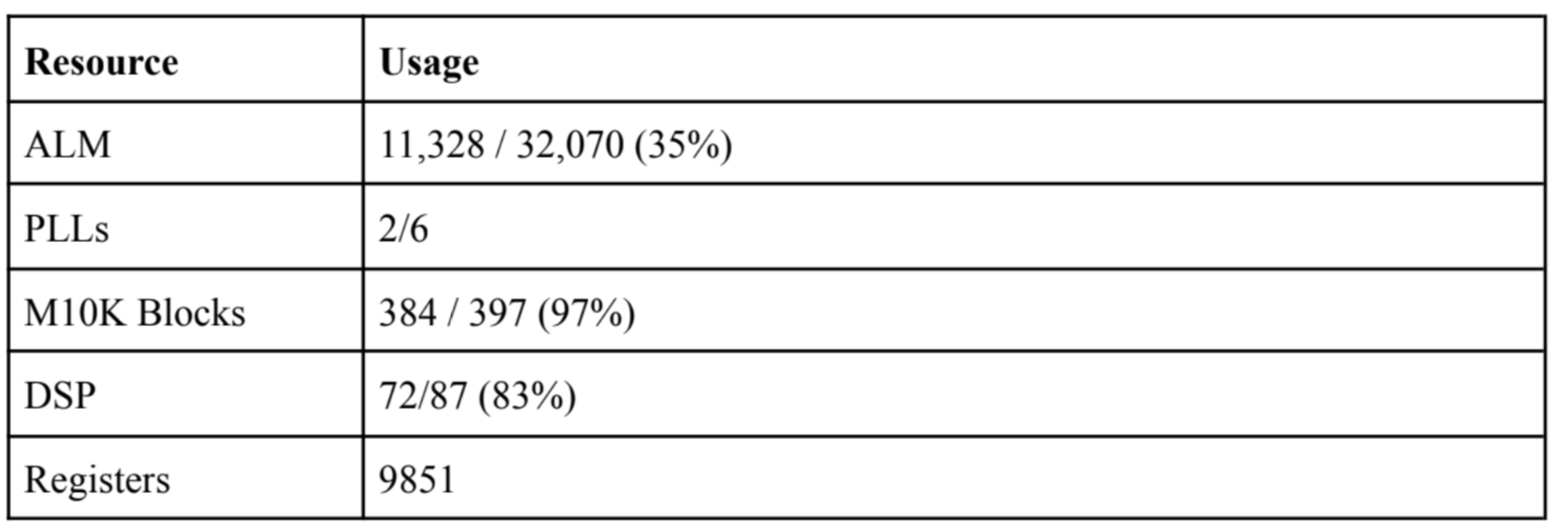

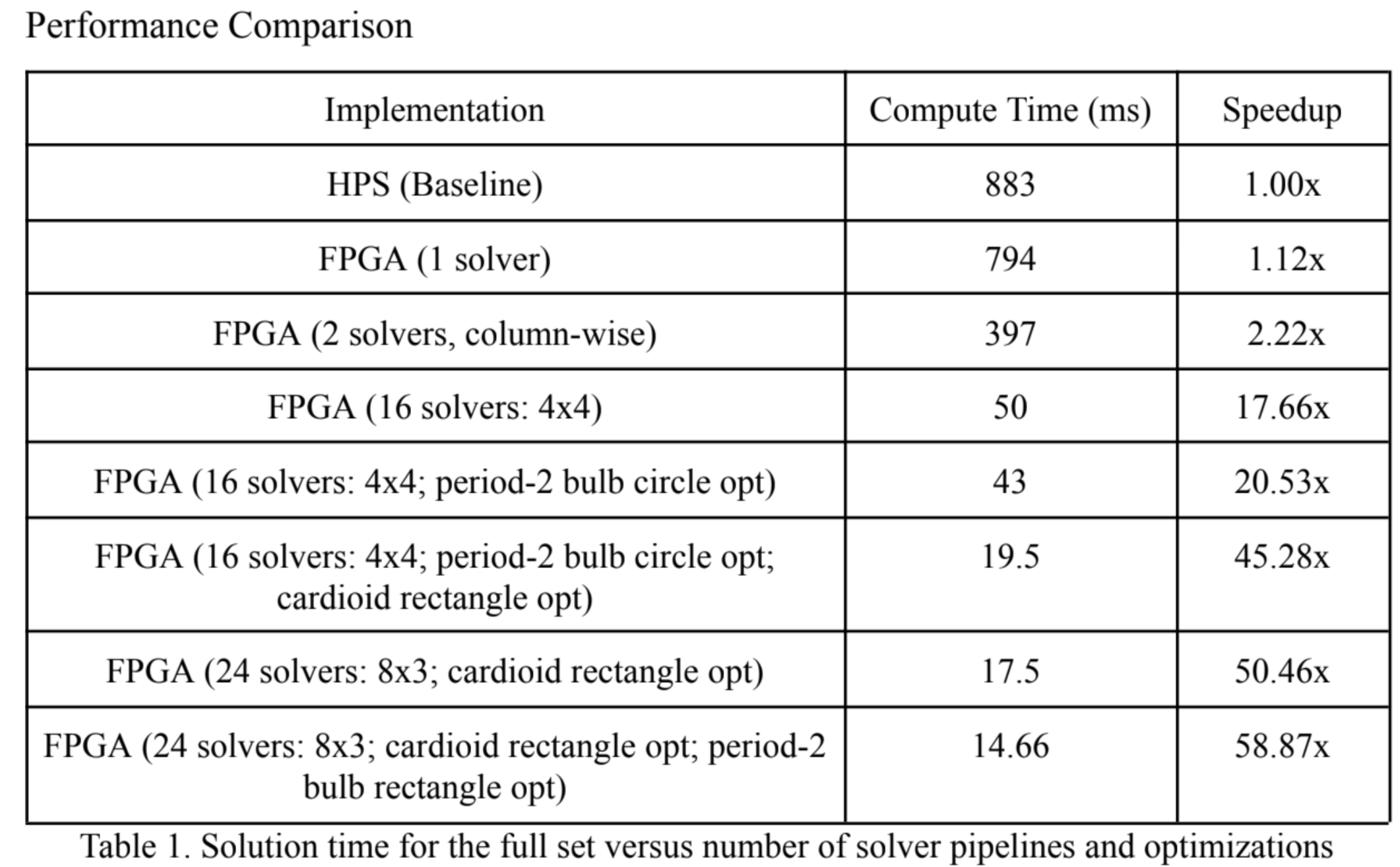

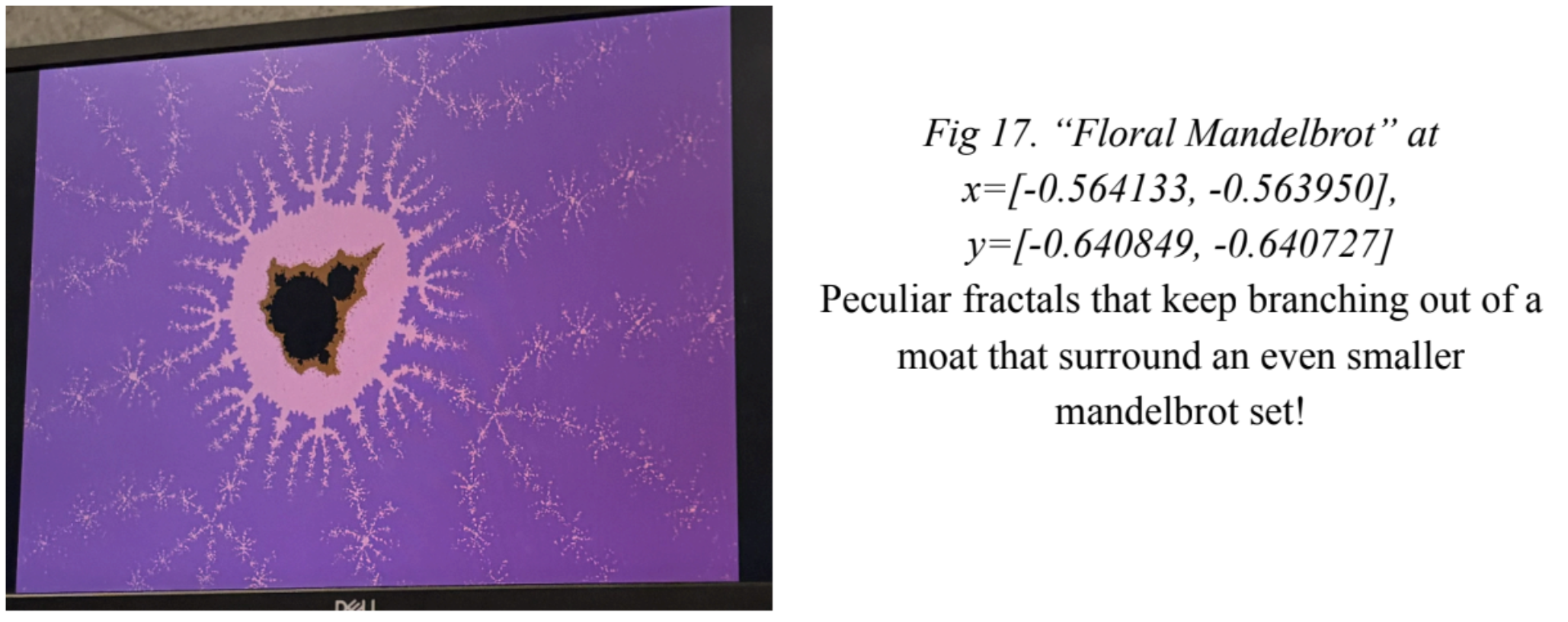

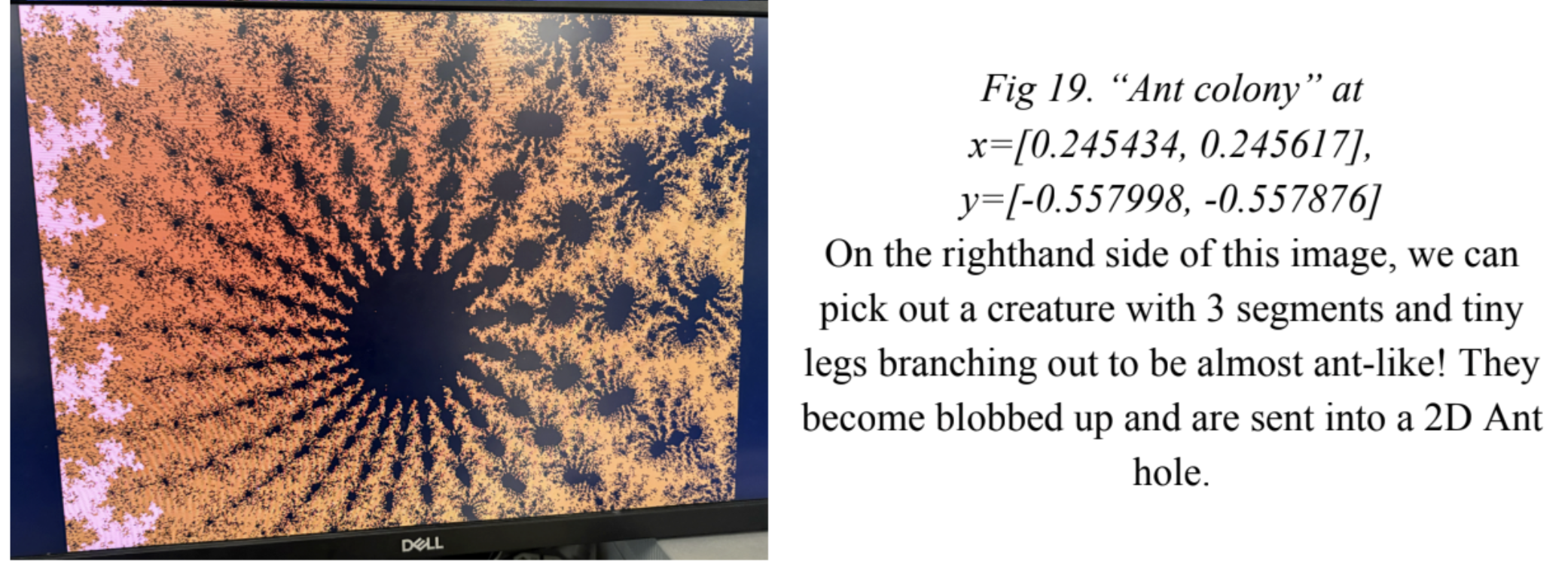

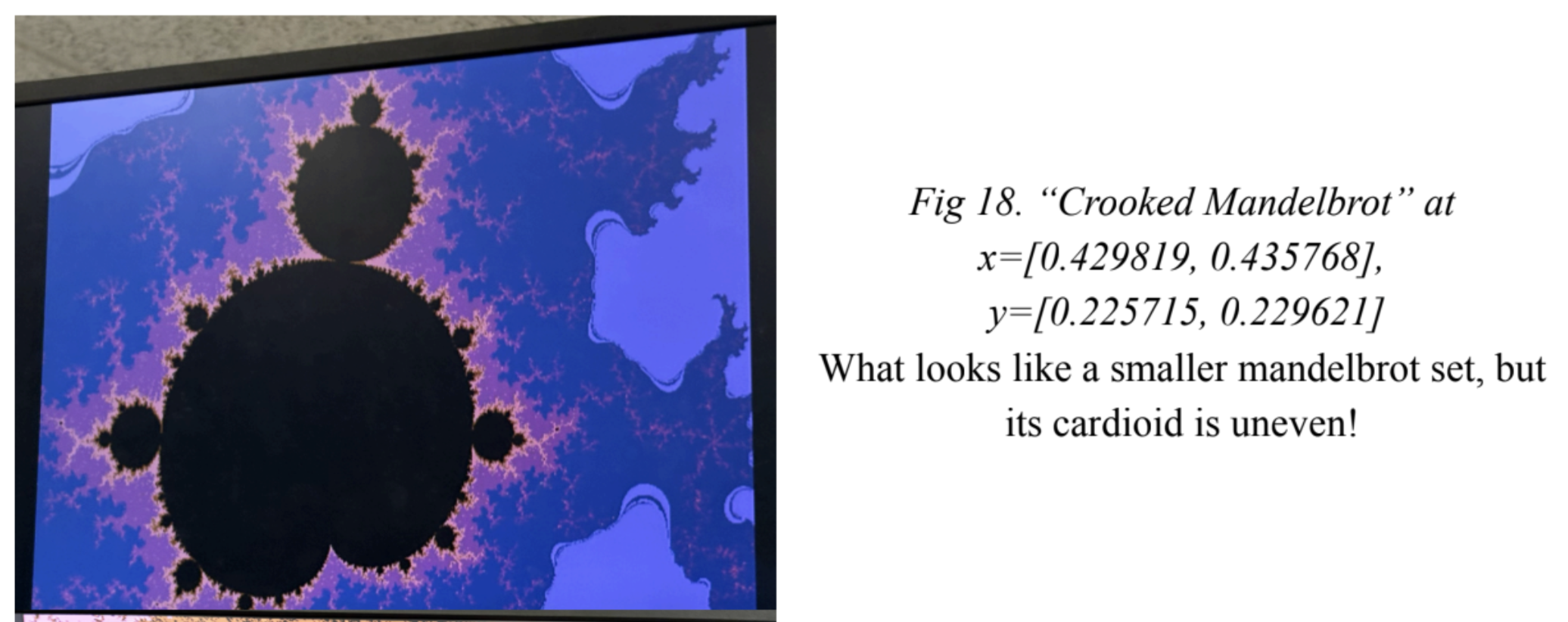

As part of Cornell's Hardware Acceleration via FPGA course (ECE 5760), I designed and implemented a Mandelbrot Set Visualizer on an Intel Altera DE1-SoC FPGA. The project involved parallelizing the computation of pixel colors for VGA output, resulting in a significant performance improvement over a software implementation. I utilized Intel Quartus for hardware design, ModelSim for simulation, and Qsys for system integration. The final design successfully rendered the Mandelbrot set in real-time on a VGA display, demonstrating the power of hardware acceleration for computationally intensive tasks.