Project information

- Project date: February 1, 2026 - March 1, 2026

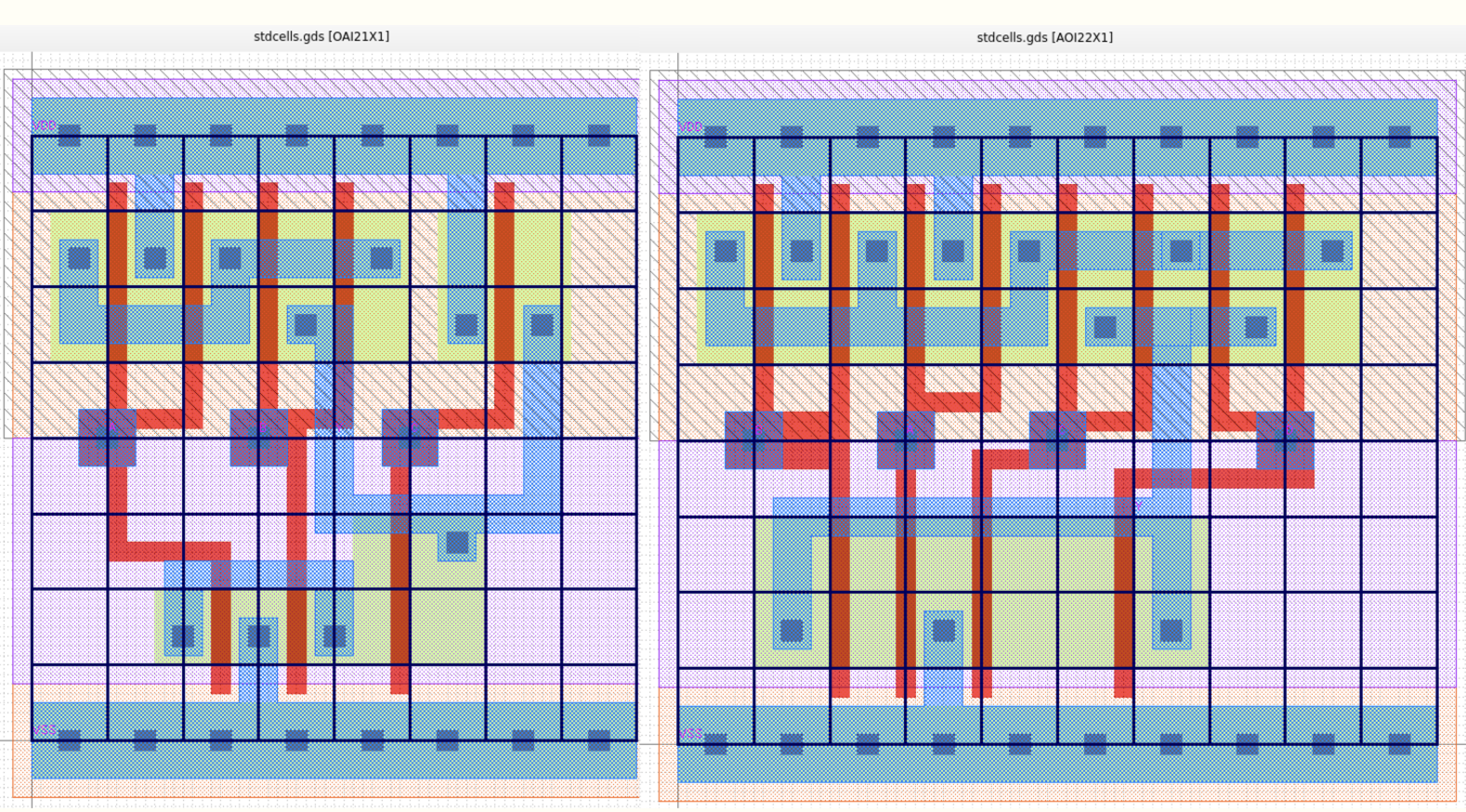

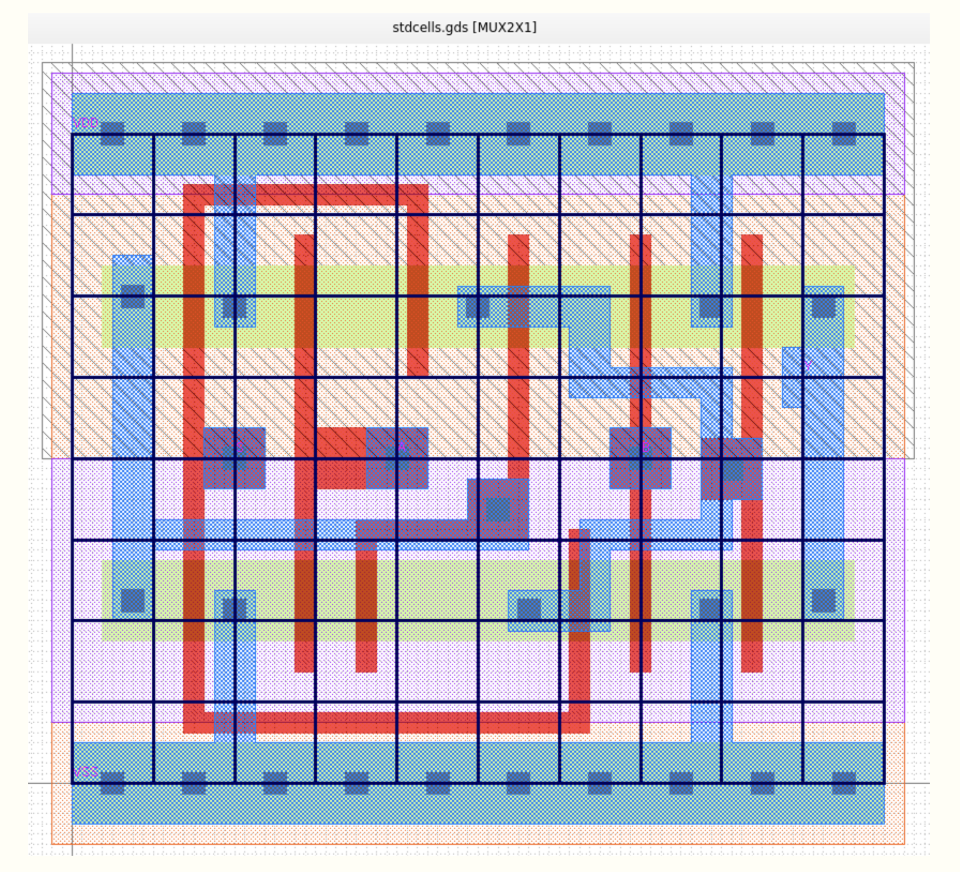

- Tools: Icarus Verilog (GL sim, 4 state RTL), Ngspice (Schem Sim), Klayout (DRC, LVS, RCX), Verilator (2 state RTL), Our Custom Flow Synthesis, Our Custom Place & Route

- Link to Presentation

Summary

Popcount on Hardware:

ASIC Design

Digital ASIC Design Project

As part of Cornell’s Digital ASIC Design course (ECE 6745), my group and I designed a 1umx1um ASIC in the TSMC 180nm node for tape out this comming summer.

We created a custom flow for synthesis, place and route, and signoff, and used a variety of tools including Icarus Verilog, Ngspice, Klayout, and Verilator to design and verify our chip.

Our chip implements a popcount unit that counts the number of 1s in a 8-bit input, which is a common operation in many applications such as machine learning and cryptography. we are excited to see our chip come to life in the coming months!