Project information

- Project date: April 21, 2025- May 17, 2025

- Tools: Cadence Virtuoso (Schematic & Layout)

- Link to Github Repo

- Link to Final Report

- Link to Final Poster

Summary

ALUminati:

High-Speed 4-Bit Arithmetic Logic Unit (ALU) Design

Digital VLSI Final Project

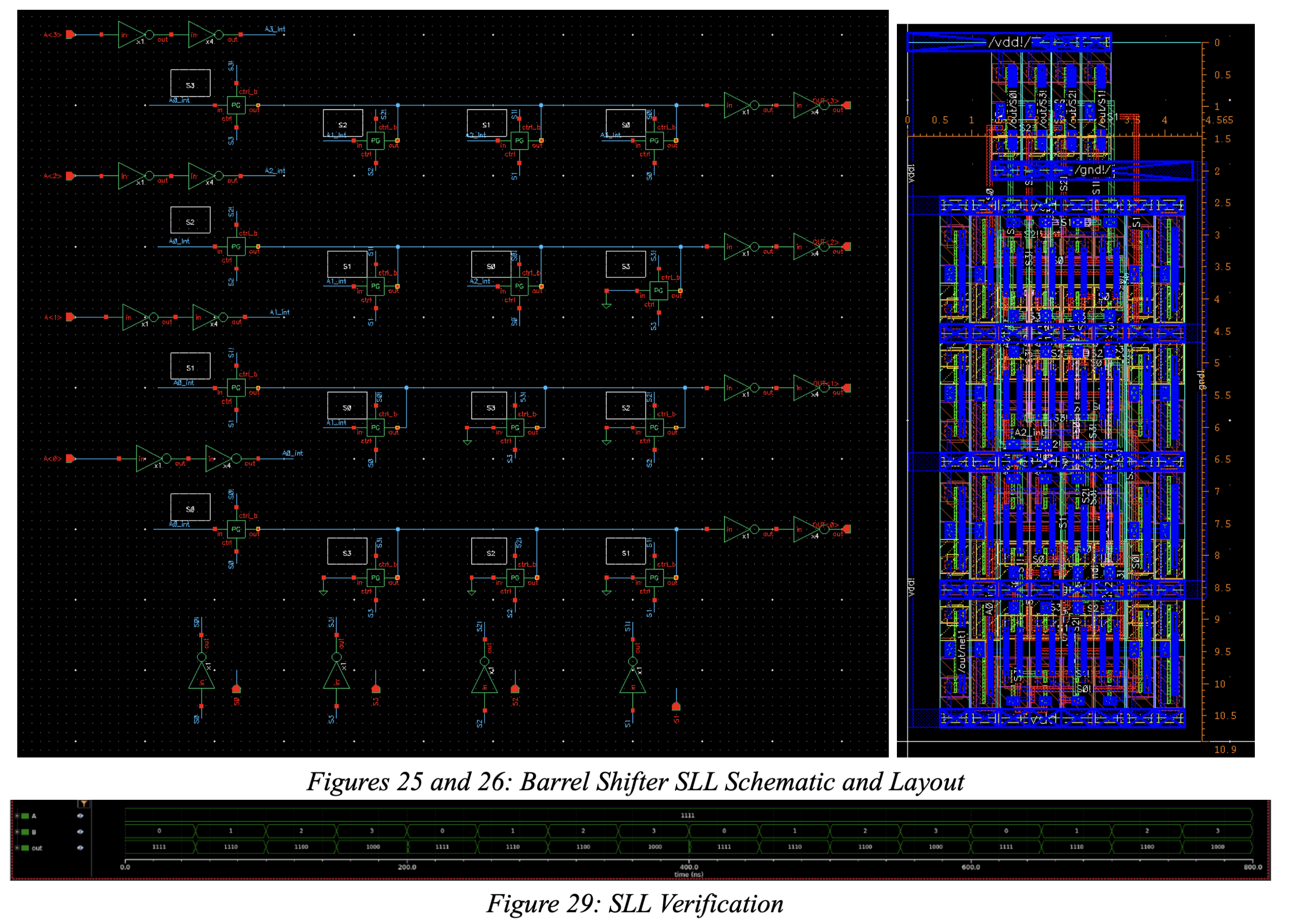

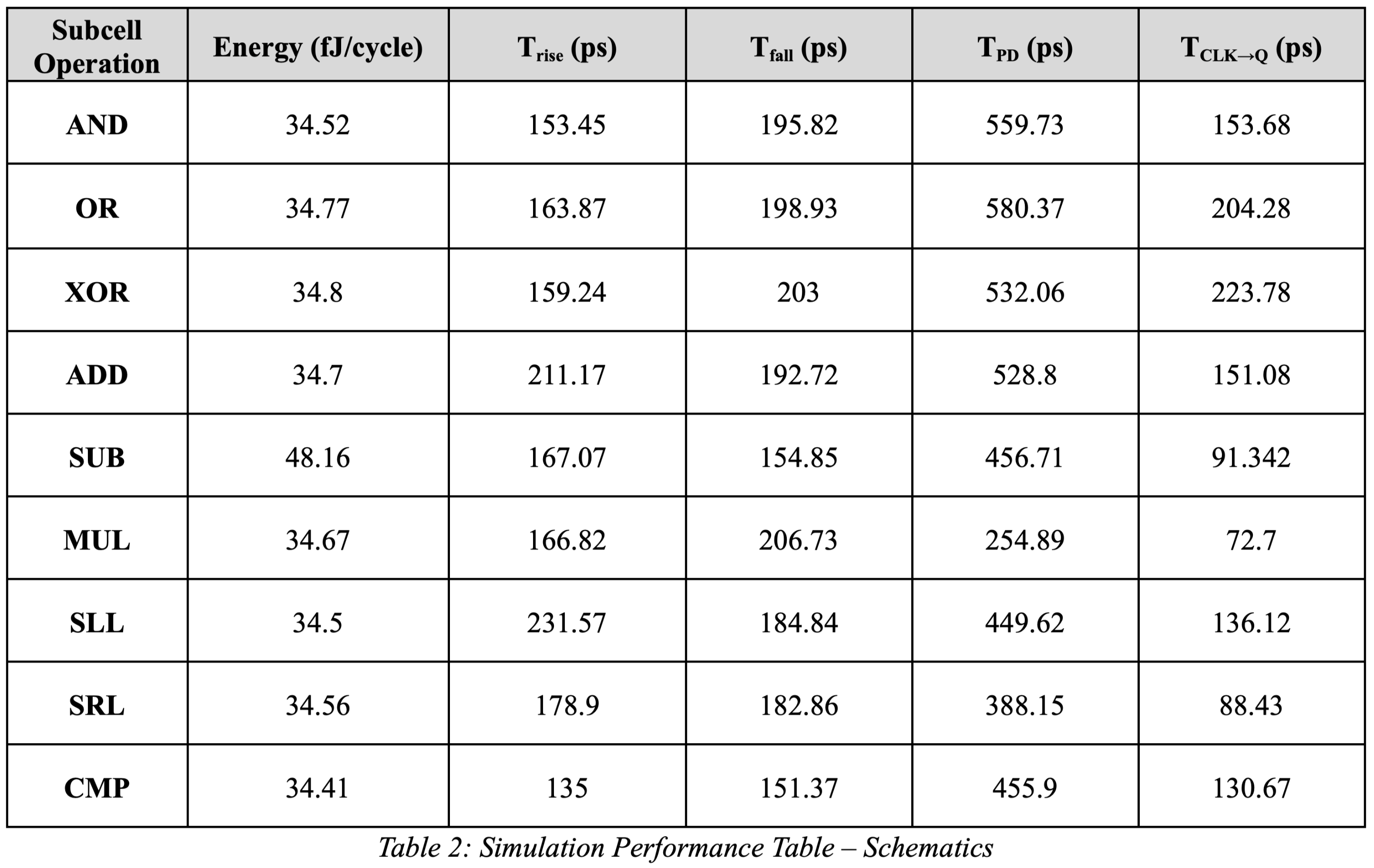

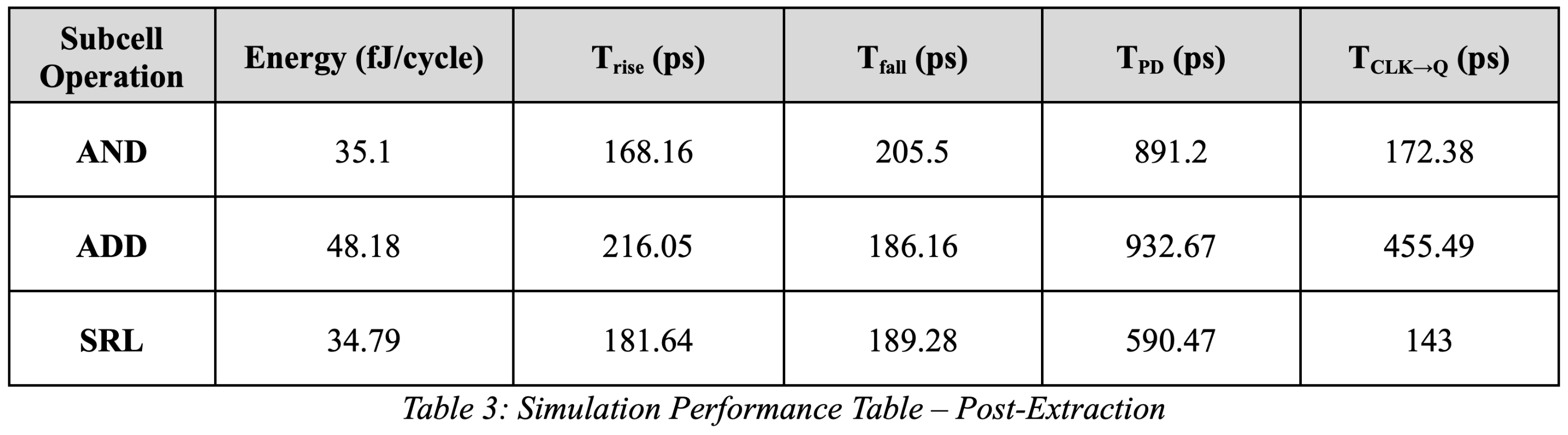

As part of Cornell’s Digital VLSI course (ECE 4740), my team and I designed a high-speed 4-bit Arithmetic Logic Unit (ALU) capable of performing 10 operations, including arithmetic (ADD, SUB, MUL), bitwise (AND, OR, XOR), logical shifts (SLL, SRL), and comparisons (G, GEQ). Our focus was on optimizing performance using dynamic logic for speed and exploring alternative logic for power efficiency.

First, we drew and verified circuits via simulations. Then, we did transistor layout, following Design Rule Check (DRC) and Layout Versus Schematic (LVS) checks.

Key features included a custom-designed ripple carry adder with mixed dynamic-static logic, area-efficient barrel shifters, and verified subcell integration through SPICE simulation. The project emphasized delay optimization, glitch mitigation, and layout-aware design—showcasing practical applications of VLSI techniques in a classic digital system.